1. Jurnal[Back]

2. Alat dan Bahan[Back]

a. 74LS122

b. 7474

c. VCC

d. Logic Probe

e. Switch

f. Ground

g. Jumper

h.Clock

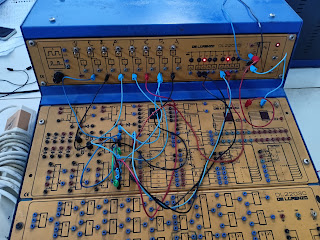

3. Rangkaian Simulasi[Back]

4. Prinsip Kerja Rangkaian[Back]

Pada percobaan pertama kita melihat output yang dihasilkan oleh input yang masuk ke J-K flip flop dan D flip flop.

Pada switch untuk kaki bagian atas yang berlogika 1 terhubung langsung ke VCC dan yang satu lagi berlogika 0 karena terhubung langsung ke Ground. Swicth 2, 3 dan 4 untuk J,clock dan K. Sedangkan untuk B0 dan B1 untuk R dan S pada J-K flip flop dan D flip flop.

Ketika logika input diatur pada B0=0, dialirkan ke input R , B1=1 dialirkan ke input S. Dan SPDT lainnya dont care, saat percobaan dont care dibuat dalam kondisi 0. Output yang di hasilkan di J-K flipflop yaitu 0 di Q dan 1 di Q'. Sedangkan di D Flip Flop outputnya 0 di Q dan 1 di Q'.

Ketika logika input diatur pada B0=1 dan B1=0. SPDT lainnya Dont care atau saat percobaan di buat 0, menghasilkan output di J-K flip flop 0 untuk Q dan 1 untuk Q'. Di D flipflop outputnya 0 di Q dan 1 di Q'.

Ketika logika input pada B0 dan B1 sama-sama 0 menghasilkan keadaan terlarang dimana semua outputnya itu berlogika 1, baik di J-K flip flop maupun D flip flop.

Ketika logika input pada B0 dan B1 sama-sama 1 menghasilkan keadaan tetap dimana sesuai dengan output sebelumnya.

5. Video Rangkaian[Back]

6. Analisa[Back]

a. Bagaimana jika B0 dan B1 sama-sama diberi logika 0, apa yang akan terjadi pada rangkaian?

Ketika B0 dan B1 diberi logika 0, maka pada rangkaian akan terjadi kondisi terlarang dimana hasil outputnya semuanya 1, baik di JK flip flop maupun D flip flop.

b. Bagaimana jika B3 diputuskan/tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian?

Ketika B3 diputuskan atau tidak dihubungkan maka output itu tetap atau sesuai dengan input R dan S, jika R logika 1 maka Q itu juga 1 atau bisa dikatakan clock tersebut off.

c. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada flip flop?

Kondisi toggle pada flip flop yaitu kondisi dimana output dari flip flop yang merupakan komplemen atau kebalikan dari output sebelumnya misal output sebelumnya 0, 1 maka selanjutnya menjadi 1,0.

Kondisi not change yaitu ketika nilai dari R dan S nya itu bernilai 1 sehingga dalam keadaan off dan outputnya tetap nilainya dengan nilai sebelumnya.

Kondisi terlarang yaitu kondisi dimana ketika B1 dan B0 nya yaitu 0 sehingga menghasilkan nilai outputnya 1 karena R dan S nya mendapat input 0.

b

7. Link Download[Back]

Download Rangkaian[disini]

Download Video Percobaan[disini]

Download HTML[disini]

Tidak ada komentar:

Posting Komentar