1. Jurnal[Back]

2. Alat dan Bahan[Back]

a. Gerbang Logika NOT

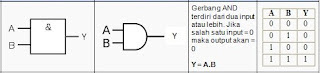

b. Gerbang Logika AND

c. Gerbang Logika OR

d. Gerbang Logika XOR

e. Gerbang Logika NAND

f. Gerbang Logika NOR

g. Gerbang Logika XNOR

h. VCC

i. Logic Probe

j. Switch

k. Ground

l. Jumper

m.Clock

3. Rangkaian Simulasi[Back]

Percobaan 1

Percobaan 2

4. Prinsip Kerja Rangkaian[Back]

Pada percobaan pertama kita melihat output yang dihasilkan oleh input yang masuk ke berbagai gerbang logika, disini input yang digunakan yaitu VCC dan untuk gerbang logika ada 7 macam diantaranya Gerbang logika NOT, AND, OR, XOR, NAND, NOR dan XNOR.

Pada switch untuk kaki bagian atas yang berlogika 1 terhubung langsung ke VCC dan yang satu lagi berlogika 0 karena terhubung langsung ke Ground. Swicth saatu diberi nama B1 dan Switch kedua itu diberi nama B0, kaki NOT terhubung ke B1 dan satu kaki dari masing- masing gerbang terhubung ke B1 sedangkan kaki lainnya terhubung ke B0.

Ketika logika input diatur pada B1=0, dialirkan ke input gerbang NOT sehingga output dari gerbang NOT akan berlogika 1 dikarenakan output dari gerbang NOT adalah kebalikan dari inputnya.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang AND sehingga output dari gerbang AND akan berlogika 0 dikarenakan gerbang AND akan mengalikan semua input yang masuk. Sehingga, jika salah satu input berlogika 0 maka outputnya akan berlogika 0.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang OR sehingga output dari gerbang OR akan berlogika 1 dikarenakan gerbang OR akan menjumlahkan semua input yang masuk. Sehingga, jika salah satu input berlogika 1 maka outputny akan berlogika 1.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang XOR sehingga ouput dari gerbang XOR akan berlogika 1 dikarenakan gerbang XOR akan menjumlahkan semua input yang masuk dan outputnya sesuai dengan hasil dari penjumlahan input dari gerbang X-OR. Jika hasil penjumlahan input Ganjil, maka output dari gerbang XOR akan berlogika 1. Jika hasil penjumlahan input Genap, maka output dari gerbang XOR akan berlogika 0.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang NAND sehingga output dari gerbang NAND akan berlogika 0 dikarenakan gerbang NAND akan mengalikan semua input yang masuk dan output dari gerbang NAND adalah kebalikan dari hasil perkalian dari inputnya. Jika salah satu input berlogika 0 maka outputnya akan berlogika 1.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang NOR sehingga output dari gerbang NOR akan berlogika 0 dikarenakan gerbang NOR akan menjumlahkan semua input yang masuk dan output dari gerbang NOR adalah kebalikan dari hasil penjumlahan inputnya. Jika salah satu input berlogika 1 maka outputnya akan berlogika 0.

Ketika logika input diatur pada B1=0 dan B0=1, dialirkan ke input gerbang XNOR sehingga output dari gerbang XNOR akan berlogika 0 dikarenakan gerbang XNOR akan menjumlahkan semua input yang masuk dan outputnya sesuai dengan hasil dari penjumlahan input dari gerbang XNOR. Jika hasil penjumlahan input = Ganjil, maka output dari gerbang XNOR akan berlogika 0. Jika hasil penjumlahan input = Genap, maka output dari gerbang XNOR akan berlogika 1.

Untuk tabel kedua di percobaan pertama kita ganti input yang awalnya dari VCC menjadi clock, untuk clock ini kta melihat gelombang yang terbentuk dari setiap gerbang logika. Kaki NOT yang awalnya dihubungkan ke B1 di pindahkan ke clock, dan juga kaki dari gerbang lainnya yang awalnya terhubung ke B0 dipindahkan ke clock.

Ketika logika input untuk NOT dari clock di outputnya itu berubah dari 1 lalu ke 0 dan begitu seterusnya, sehingga gelombang persegi dimulai dari 1.

Ketika logika input B1=0 dan clock maka untuk gerbang logika AND itu dimulai dari 0 dan tidak ada perubahan logika. Ketika B1= 1 dan ada nya clock gerbang AND itu berubah dari 0 ke 1 dan begitu seterusnya.

Ketika B1=0 dan adanyua clock gerbang logika OR itu berubah dari 0 ke 1 sehingga gelombang dari 0 naik ke 1 dan seterusnya. Ketika B1=1 dan clock maka gerbang logika OR itu hanya berlogika 1.

Ketika B1=0 dan clock maka output gerbang Logika XOR itu berubah dari 0 ke 1 dan seeterusnnnya. Ketika B1=1 dan clock output gerbang XOR berubah dari 1 ke 0 sampai seterusnya.

Ketika B1=0 dan clock maka output gerbang logika NAND itu tetap di 1. Ketika B1=1 dan clock maka NAND outputnya dari 1 ke 0 dan seterusnya.

Ketika B1 = 0 dan clock maka output gerbang logika NOR itu berubah dari 1 ke 0 dan seterusnya. Ketika B1=1 dan clock maka gerbang logika itu tetap 0.

Ketika B1=0 dan clock maka output gerbang logika XNOR itu berubah dari 1 ke 0 dan seterusnya. Ketika B1=1 dan clock maka XNOR itu berubah dari 0 ke 1 dan seterusnya.

5. Video Rangkaian[Back]

6. Analisa[Back]

a. Jelaskan prinsip kerja Rangkaian dalam setiap gerbang logika, minimal 3.

- AND

- NOR

Untuk gerbang logika NOR menggunakan prinsip pertambahan yang hasilnya di NOT kan, sehingga ketika input yang masuk hasilnya berlogika 1 maka di notksn menjadi 0. Seprti di rangkaian jika input B1 dan B0 masuk berlogika 1 dan 0 maka hasilnya 1 di NOT kan menjadi 0.

- XOR

Untuk gerbang logika XOR menggunakan prinsip pertambahan eksklusif dimana kita melihat hasil penjumlahan dari input. Jika hasil penjumlahan genap maka outputnya 0, dan jika hasilnya ganjil maka outputnya 1, misal pada percobaan input B0 1 dan B1 0 maka hasilnya ganjil sehingga outputnya 1.

- OR

Untuk gerbang logika OP menggunakan prinsip penjumlahan, jadi dipercobaan jika B0 inputnya 1 dan B1 juga 1 maka outputnya 1.

7. Link Download[Back]

Download Rangkaian[disini]

Download Video Percobaan[disini]

Dowload datasheet OR[disini]

Download datasheet NOT[disini]

Download datasheet AND[disini]

Download datasheet XOR[disini]

Download datasheet NAND[disini]

Download HTML[disini]

.jpg)

.jpg)

.png)

.png)

Tidak ada komentar:

Posting Komentar